## VME MODULE

## CPU J11

User's Manual

Part Number: 32958044

PRIROČNIK UP/EN\* PVT CPU-J11

First Edition July 1986

ISKRA DELTA

© 1986, ISKRA DELTA, Ljubljana, Klagenfurt, New York

The information in this document has been carefully checked for technical accuracy. However, ISKRA DELTA makes no warranty of any kind with regard to the material in this document and assumes no responsibility for any errors that may appear in this document. ISKRA DELTA reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance, or design.

ISKRA DELTA assumes no responsibility for the use of any circuitry which is not part of an ISKRA DELTA product.

ISKRA DELTA does not convey to the purchaser of the product described herein any license under the patent rights of ISKRA DELTA or any others.

The following are trademarks of Digital Equipment Corp.:

DEC

Digita1

PDP-11

DCJ11

VME CPU J11 is a trademark of ISKRA DELTA.

# TABLE OF CONTENTS

| Chapter 1 | Introduction                              |   |

|-----------|-------------------------------------------|---|

| 1.1       | Introduction                              |   |

| 1.2       | VME CPU J11 Specifications                |   |

| 1.2.1     | . VMEbus Options                          |   |

| 1.2.2     | VMEbus Options<br>Central Processing Unit |   |

| 1.2.3     | Memory                                    |   |

| 1.2.4     | Serial Interface                          |   |

| 1.2.5     | Parallel Interface and Timers             |   |

| 1.2.6     | Real-Time Clock and Data Memory           |   |

| 1.3       | Abbreviations                             |   |

|           |                                           |   |

| Chapter 2 | Installation                              |   |

| 2.1       | Introduction                              | : |

| 2.2       | Unpacking the VME CPU J11                 | : |

| 2.3       | Configuration                             |   |

| 2.3.1     | Power-Up Options                          |   |

| 2.3.1.1   | Restart-Boot                              | - |

| 2.3.1.2   | ODT-Boot                                  |   |

| 2.3.1.3   | Auto-Boot                                 |   |

| 2.3.2     | HALT Options                              |   |

| 2.3.2.1   | ODT-HALT                                  |   |

| 2.3.2.2   |                                           |   |

| 2.3.3     | DRAMC Speed Options                       |   |

| 2.3.4     | SIZE Select Option                        |   |

| 2.3.5     | Arbiter Options                           |   |

| 2.3.5.1   | PRI                                       |   |

| 2.3.5.2   | ONE                                       |   |

| 2.3.6     | Requestor Options                        |

|-----------|------------------------------------------|

| 2.3.6.1   | ROR                                      |

| 2.3.6.2   |                                          |

| 2.3.7     | Interrupt Handler Options                |

| 2.3.8     | BSYSCLK                                  |

| 2.4       | Board Installation                       |

| 2.4.1     | Console Terminal Connection              |

| 2.4.2     | Printer Connection                       |

| 2.4.3     | VMEbus Connection                        |

| 2.4.4     | Maintenance Indicators and Switches      |

| 2.4.4.1   | Power-Up Sequence                        |

| 2.4.4.2   | Power-Up Sequence                        |

| 2.5       | Console Online Debugging Technique (ODT) |

| 2.5.1     | Exiting the Micro-ODT Sequence           |

| Chapter 3 | Architecture                             |

|           |                                          |

| 3.1       | Introduction                             |

| 3.2       | The Central Processing Unit              |

| 3.3       | Local Memory                             |

| 3.4       | Serial Interface                         |

| 3.5       | Parallel Interface                       |

| 3.5.1     | Parallel Printer Port                    |

| 3.5.2     | Counter/Timers                           |

| 3.6       | Real-Time Clock                          |

| 3.6.1     | Line Clock Generator                     |

| 3.6.2     | Time-of-Day Clock and Time-of-Day Alarm  |

| 3.6.3     | General-Purpose Data Memory              |

| 3.7       | Boot Logic                               |

| 3.8       | Interrupt Handler                        |

| 3.8.1     | Single-Handler Systems                   |

| 3.8.2     | Distributed-Handler Systems              |

| 3.9       | Bus Arbitration                          |

| 3.9.1     | Single-Level Arbitration (Local Arbiter) |

| 3 9 2     | Four-Level Arbitration (Global Arbiter)  |

| Chapter 4 | Programming Model                              |

|-----------|------------------------------------------------|

| 4.1       | VME CPU J11 Programming Model 4-1              |

| 4.1.1     | General-Purpose Registers 4-2                  |

| 4.1.2     | System-Control Registers 4-2                   |

| 4.1.2.1   | Processor Status Word Register 4-3             |

| 4.1.2.2   | Program Interrupt Request                      |

|           | Register (PIRQ) 4-4                            |

| 4.1.2.3   | Processor Error Register (PER) 4-5             |

| 4.1.3     | Memory-Management Registers 4-6                |

| 4.1.3.1   | Page Address Register (PAR) 4-6                |

| 4.1.3.2   | Page Description Register (PDR) 4-7            |

| 4.1.3.3   | Memory Management Status Register 0 (MMR0) 4-8 |

| 4.1.3.4   | Memory Management Status Register 1 (MMR1) 4-9 |

| 4.1.3.5   | Memory Management Status Register 2 (MMR2) 4-9 |

| 4.1.3.6   | Memory Management Status Register 3 (MMR3) 4-1 |

| 4.1.4     | Memory-System Register 4-1                     |

| 4.1.5     | Floating-Point Registers 4-1                   |

| 4.1.5.1   | The Floating-Point Status Register 4-1         |

| 4.1.5.2   | The Floating-Point Exception                   |

|           | Code Register (FEC) 4-1                        |

| 4.1.5.3   | The Floating-Point Exception                   |

|           | Address Register (FEA) 4-1                     |

| 4.2       | Addressing Modes Summary 4-1                   |

| 4.2.1     | Direct Addressing Modes 4-1                    |

| 4.2.2     | Indirect Addressing Modes 4-1                  |

| 4.2.3     | Program Counter Addressing Modes 4-1           |

| 4.3       | Instruction Set Summary 4-1                    |

| 4.3.1     | Single-Operand Instructions 4-1                |

| 4.3.1.1   | General Instructions 4-1                       |

| 4.3.1.2   | Shift and Rotate Instructions 4-1              |

| 4.3.1.3   | Multiple Precision Instructions 4-1            |

| 4.3.1.4   | PS Word Operator Instructions 4-1              |

| 4.3.2     | Double-Operand Instructions 4-1                |

| 4.3.2.1   | General Instructions 4-1                       |

| 4.3.2.2   | Logical Instructions 4-1                       |

| 4.3.2.3   | Program Control Instructions 4-1               |

| 4.3.2.4   | Trap and Interrupt Instructions 4-1            |

| 4.3.2.5   | Miscellaneous Program Control                  |

|           | Instructions 4-1                               |

| 4.3.2.6   | Miscellaneous Instructions 4-1                 |

| 4.3.2.7   | Condition Code Operators 4-1                   |

| 4.3.3     | Floating-Point Instructions 4-2                |

|           |                                                |

| 4.4     | Serial Interface                         |

|---------|------------------------------------------|

| 4.4.1   | The Receiver Control/Status Register     |

| 4.4.2   | The Receiver Buffer Register (RBUF)      |

| 4.4.3   | The Transmitter Control/Status           |

|         | Register (XCSR)                          |

| 4.4.4   | The Transmitter Buffer Register (XBUF)   |

| 4.5     | Console Online Debugging Technique (ODT) |

| 4.5.1   | Slash (ASCII 057)                        |

| 4.5.2   | RETURN (ASCII 015)                       |

| 4.5.3   | Line Feed (ASCII 012)                    |

| 4.5.4   | Internal Register Designator             |

|         | (ASCII 044 or 122)                       |

| 4.5.5   | Processor Status Word Designator         |

|         | (ASCII 123)                              |

| 4.5.6   | Go (ASCII 107)                           |

| 4.5.7   | Proceed (ASCII 120)                      |

| 4.5.8   | Binary Dump (ASCII 23)                   |

| 4.6     | Parallel Interface                       |

| 4.6.1   | The Master Control Registers             |

| 4.6.1.1 | The Master Interrupt Control             |

|         | Register                                 |

| 4.6.1.2 | The Master Configuration                 |

|         | Control Register                         |

| 4.6.2   | Port Specification Registers             |

| 4.6.2.1 | The Port Mode Specification              |

|         | Registers                                |

| 4.6.2.2 | The Port Handshake Specification         |

|         | Registers                                |

| 4.6.2.3 | The Port Command and Status              |

|         | Registers                                |

| 4.6.3   | Bit-Path Definition Registers            |

| 4.6.3.1 | The Data Path Polarity Registers         |

| 4.6.3.2 | The Data Direction Registers             |

| 4.6.3.3 | The Special I/O Control Registers        |

| 1.6.4   | The Port Data Registers                  |

| .6.5    | The Pattern-Definition Registers         |

| .6.6    | The Counter/Timer Registers              |

| .6.6.1  | The Counter/Timer Command and            |

|         | Status Registers                         |

| .6.6.2  | The Counter/Timer Mode                   |

|         | Specification Registers                  |

| .6.6.3  | The Counter/Timer Current Count          |

|         | Registers                                |

| .6.6.4  | The Counter/Timer Time-Constant          |

|         | Registers                                |

| .6.7    | The Interrupt Vector Registers           |

| .6.7.1  | The Interrupt Vector Register            |

| .6.7.2  | The Current Vector Register              |

| 4.7        | Real-Time Clock Programming | 4-39 |

|------------|-----------------------------|------|

| 4.7.1      | Real-Time Clock: Register A | 4-40 |

| 4.7.2      | Real-Time Clock: Register B | 4-41 |

| 4.7.3      | Real-Time Clock: Register C | 4-42 |

| 4.7.4      | Real-Time Clock: Register D | 4-43 |

| 4.8        | Boot Programming            | 4-43 |

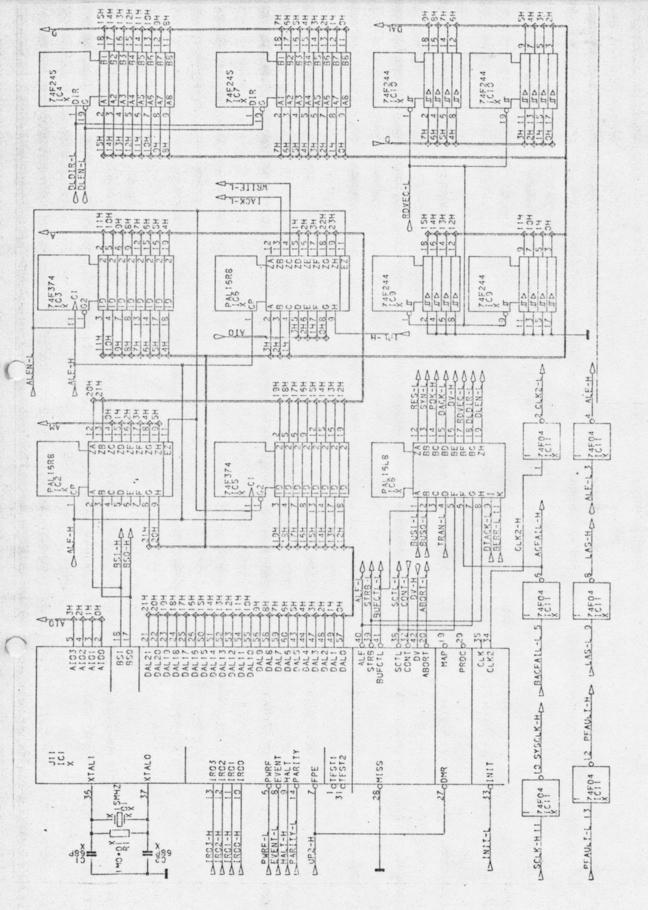

| Appendix A | Schematics                  | A-1  |

| Appendix B | Related Documentation_      | B-1  |

# LIST OF FIGURES

| Chapter 1   |                                                                  |

|-------------|------------------------------------------------------------------|

| Figure 1-1. | VME CPU J11                                                      |

| Chapter 2   |                                                                  |

| Figure 2-1. | VME CPU J11 Configurable Jumpers and PALs                        |

| Figure 2-2. | Jumper Configuration for Local Memory Access<br>on the BR1 Level |

| Figure 2-3. | Jumper Configuration for Local Memory Access<br>on the BR2 Level |

| Figure 2-4. | Jumper Configuration for the ONE Arbiter Option                  |

| Figure 2-5. | VME CPU Jll Switch, LEDs, and Peripheral<br>Connectors           |

| Figure 2-6. | VME CPU J11 Power-Up Sequence                                    |

| Figure 2-7. | VME CPU J11 Power-Down Sequence                                  |

| Figure 2-8. | The Exit Micro-ODT Sequence                                      |

| Chapter 3   |                                                                  |

| Figure 3-1. | VME CPU J11 Architecture                                         |

| Chapter 4   |                                                                  |

| Figure 4-1. | Visible Registers                                                |

| Table 2-9  | . Pin Specifications for the Pl Connector                | 2    |

|------------|----------------------------------------------------------|------|

| Table 2-1  | O. VME CPU J11 LED Functions                             | _ 2  |

| Table 2-1  | 1. LED Readings During System Failure                    | _ 2  |

| Table 2-1: | 2. ODT Mode Commands                                     | _ 2- |

| Observe /  |                                                          |      |

| Chapter 4  |                                                          |      |

| Table 4-1. | System-Control Register Addresses                        | _ 4- |

| Table 4-2. | Processor Status Word Register Bit Description           | _ 4- |

| Table 4-3. | Program Interrupt Request Register Bit Description       | 4-   |

| Table 4-4. | Processor Error Register Bit Description                 | 4-   |

| Table 4-5. | Memory-Management Register Addresses                     | 4-   |

| Table 4-6. | Page Address Register Bit Description                    | 4-   |

| Table 4-7. | Page Description Register Bit Description                | 4-   |

| Table 4-8. | Memory Management Status Register 0 Bit<br>Description   | 4-   |

| Table 4-9. | Memory Management Status Register 1 Bit<br>Description   | _ 4- |

| Table 4-10 | . Memory Management Status Register 2 Bit<br>Description | _ 4- |

| Table 4-11 | Memory Management Status Register 3 Bit Description      | _ 4- |

| Table 4-12 | Floating-Point Status Register Bit Description           | _ 4- |

| Table 4-13 | Floating-Point Exception Codes                           | _ 4- |

|            | Direct Addressing Modes                                  |      |

|            | Indirect Addressing Modes                                |      |

|            | Program Counter Addressing Modes                         |      |

|            | Addresses for the Serial Interface Registers             |      |

|            | Receiver Control/Status Register Bit<br>Descriptions     | 4-   |

| Tab1  | e 4-19  | . Receiver Buffer Register Bit Descriptions                     |

|-------|---------|-----------------------------------------------------------------|

| Tab1  | e 4-20  | . Transmitter Control/Status Register Bit Descriptions          |

| Tab1  | e 4-21  | . Transmitter Buffer Register Bit Descriptions _                |

| Tab1  | e 4-22  | . The ODT Commands                                              |

| Tab1  | e 4-23  | . Addresses for the Parallel Interface Registers                |

| Tab1  | e 4-24  | Master Control Register Addresses                               |

| Tab1  | e 4-25. | Master Interrupt Control Register Bit Descriptions              |

| Table | e 4-26. | Master Configuration Control Register Bit<br>Descriptions       |

| Table | 4-27.   | Port Specification Register Addresses                           |

| Table | 4-28.   | Port Mode Specification Register Bit<br>Descriptions            |

| Table | 4-29.   | Port Handshake Specification Register Bit<br>Descriptions       |

| Table | 4-30.   | Port Command and Status Register Bit<br>Descriptions            |

| Table | 4-31.   | Code for Writing IUS, IE, IP                                    |

| Table | 4-32.   | Bit-Path Definition Register Addresses                          |

| Table | 4-33.   | Data Path Polarity Register Bit Description                     |

| Table | 4-34.   | Data Direction Register Bit Description                         |

| Table | 4-35.   | Special I/O Control Register Bit Description                    |

| Table | 4-36.   | Pattern-Definition Register Addresses                           |

|       |         | Pattern Specifications for the Pattern-<br>Definition Registers |

| Table | 4-38.   | The Counter/Timer Command and Status Register Bit Descriptions  |

| Table | 4-39.   | Counter/Timer Mode Specification Register Bit Descriptions      |

| Table |         | Real-Time Clock Addressing Map                                  |

|       |         |                                                                 |

| Table | 4-41. | Register | A | Bit | Descriptions |                   | 4-40 |

|-------|-------|----------|---|-----|--------------|-------------------|------|

| Table | 4-42. | Register | В | Bit | Descriptions | 0 0 0 0 0 0 0 0 0 | 4-41 |

| Table | 4-43. | Register | C | Bit | Descriptions |                   | 4-42 |

| Table | 4-44. | Register | D | Bit | Descriptions |                   | 4-43 |

## 1. INTRODUCTION

#### 1.1 INTRODUCTION

The VME CPU J11 is a VMEbus, DEC J11 CPU-based processor module designed for use in high-speed, real-time applications and for multiuser, multitasking environments.

# It includes the following features:

- \* DEC DC J11 CPU with 15 MHz clock frequency

- \* On-chip memory management

- \* RS-232C serial port for console interface

- \* Real-time clock and calendar

- \* 512KB dynamic RAM with parity

- \* 2 EPROM sockets for boot (512B)

- \* Parallel port for printer with Centronics interface

- \* 3 programmable timers

- \* 4-level bus arbitration logic

- \* Fixed bus time-out

- \* SYSFAIL, SYSRESET, ACFAIL, and bus error handling

- \* 4-level interrupt handler

- \* 4-LED control panel to display operating status

- \* Standard DEC console octal debugger

Figure 1-1. VME CPU J11

All devices use interrupt protocols for ease of programming and fast response. Dynamic memory is available for the CPU and other modules through the VMEbus interface.

The VME CPU J11 can be used in single- and multiprocessor configurations through jumpers and PALs.

The VME CPU J11 is a multi-layered, printed circuit board (Figure 1-1) with on-board power and ground planes to minimize noise and provide a reliable, industrial-grade product. VME CPU J11 is fully software-compatible with all PDP-11 computers.

#### 1.2 VME CPU J11 SPECIFICATIONS

#### 1.2.1 VMEbus OPTIONS

Table 1-1 lists specifications for VMEbus options on the VME CPU J11.

Table 1-1. VMEbus Option Specifications

| Characteristic            | Specification                                                                                                          |

|---------------------------|------------------------------------------------------------------------------------------------------------------------|

| Address Bus Size          | A24 Haster, A24 Slave                                                                                                  |

| Data Bus Size             | D16 Haster, D16 Slave                                                                                                  |

| Time-Out                  | 22 μs                                                                                                                  |

| Arbiter Options           | PRI, ONE (STAT)                                                                                                        |

| Requester Options         | R(3)<br>RWD, ROR (STAT)                                                                                                |

| Interrupt Handler Options | IB(1-3) or IB(4-7) (STAT)                                                                                              |

| Operating Temperature     | 0 - 55 degrees C (32 - 131 degrees P)                                                                                  |

| Relative Humidity         | 8 - 80% (non-condensing)                                                                                               |

| Power Options             | 4A Haximum (3A Typical) at + 5 Vdc<br>30mA Haximum (20mA Typical) at +12 Vdc<br>30mA Haximum (20mA Typical) at -12 Vdc |

| Physical Configuration    | Non-expanded bus-double VME Board                                                                                      |

| Board Dimensions          | 233.4 x 160 mm (9.2 x 6.3 inches)                                                                                      |

#### 1.2.2 CENTRAL PROCESSING UNIT

Table 1-2 lists specifications for the VME CPU J11 CPU.

Table 1-2. VME J11 CPU Specifications

| Characteristic  | Specification |  |

|-----------------|---------------|--|

| Device Type     | DEC DC J11-AC |  |

| Clock Frequency | 15 MBz        |  |

| Data Width      | 16 bits       |  |

#### 1.2.3 MEMORY

Table 1-3 lists specifications for VME CPU J11 memory.

Table 1-3. VME CPU J11 Memory Specifications

| Characteristic  | Specification                                      |

|-----------------|----------------------------------------------------|

| Device Type     | Dynamic RAN 64K x 1 or 256K x 1 and 2K x 8 EPRON . |

| Hemory Size     | 128KB or 256KB RAH and 4KB EPROS                   |

| Error Detection | Byte parity (RAM only)                             |

#### 1.2.4 SERIAL INTERFACE

Table 1-4 lists specifications for the VME CPU J11 serial interface.

Table 1-4. VME CPU J11 Serial Interface Specifications

| Characteristic                | Specification                                                                                                                     |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| Function                      | Asynchronous, full duplex, serial line                                                                                            |  |

| Device Type                   | OART AY-3-1015D                                                                                                                   |  |

| Architecture<br>Compatibility | DEC "DL" compatible                                                                                                               |  |

| Transmission Rate             | 9600 Baud (fixed)                                                                                                                 |  |

| Transmission Format           | 8 bits per character, 1 stop bit, no parity (fixed)                                                                               |  |

| Electrical Interface          | RS-232C data lines (RXD, TXD)                                                                                                     |  |

| fechanical Interface          | Standard 25-pin DB 25S EIA connector (DTE): pin 1 = power ground pin 2 = transmit data pin 3 = receive data pin 7 = signal ground |  |

# 1.2.5 PARALLEL INTERFACE AND TIMERS

Table 1-5 lists specifications for the VME CPU J11 parallel interface and timers.

Table 1-5. VME CPU J11 Parallel Interface and Timer Specifications

| Characteristic       | Specification                                                  | 4 2 15 |

|----------------------|----------------------------------------------------------------|--------|

| Function             | Parallel 8-bit output port,<br>3 16-bit general-purpose timers | 40.7   |

| Device Type          | CIO 28536                                                      |        |

| Clock Frequency      | 4 MBz                                                          |        |

| Compatibility        | Centronics-compatible parallel port                            |        |

| Mechanical Interface | Centronics 36-pin connector                                    |        |

# 1.2.6 REAL-TIME CLOCK AND DATA MEMORY

Table 1-6 lists specifications for the VME CPU J11 real-time clock and data memory.

Table 1-6. VME CPU J11 Real-Time Clock and Data Memory Specifications

| Characteristic | Specification                                     |

|----------------|---------------------------------------------------|

| Function       | System clock, date, alarm, 50B static CMOS memory |

| Device Type    | RTC MC146818                                      |

## 1.3 ABBREVIATIONS

The following abbreviations are used in this manual:

| Abbreviation | Heans                                     |  |

|--------------|-------------------------------------------|--|

| AF           | Alarm Interrupt Flag                      |  |

| AIE          | Alarm Interrupt Enable                    |  |

| BCD          | Binary Coded Decimal                      |  |

| BSYSCLK      | System Clock                              |  |

| CIB          | Count in Progress                         |  |

| CSC          | Continuous Single Cycle                   |  |

| CT VIS       | Counter/Timer Vector Includes Status      |  |

| CTIE         | Counter/Timer 1 Enable                    |  |

| CT2E         | Counter/Timer 2 Enable                    |  |

| CT3E         | Counter/Timer 3 Enable                    |  |

| DCS          | Output Duty Cycle Selects                 |  |

| DD           | Data Direction                            |  |

| DDP          | Data Path Polarity                        |  |

| DEC          | Digital Equipment Corporation             |  |

| DLC          | Disable Lower Chain                       |  |

| DM           | Data Mode *                               |  |

| DRANC        | Dynamic RAM Controller                    |  |

| DSE          | Daylight Savings Enable                   |  |

| DTE          | Deskew Timer Enable                       |  |

| ECE:         | External Count Enable                     |  |

| EGE          | External Gate Enable                      |  |

| EOE          | External Output Enable                    |  |

| ERR          | Interrupt Error                           |  |

| ETE          | External Trigger Enable                   |  |

| FEA          | Floating-Point Exception Address Register |  |

| FEC          | Floating-Point Exception Code Register    |  |

| FID          |                                           |  |

| FPS          | Floating-Point Status Register            |  |

|              |                                           |  |

| Abbreviation | Reans                                      | 100 |    | 1100 | 200 |

|--------------|--------------------------------------------|-----|----|------|-----|

| GCB          | Gate Command Bit                           | _   | 99 |      |     |

| GPR          | General-Purpose Registers                  |     |    |      |     |

| RTS          | Handshake-Type Specification Bits          |     |    |      |     |

| IC           | Integrated Circuit                         |     |    |      |     |

| IE           | Interrupt Enable                           |     |    |      |     |

| IH           | Interrupt Handler                          |     |    |      |     |

| IOE          | Interrupt on Error                         |     |    |      |     |

| INO          | Interrupt on Match Only                    |     |    |      |     |

| IP           | Interrupt Pending                          |     |    |      |     |

| IRF          | Input Desister Pull                        |     |    |      |     |

| IROF         | Input Register Full                        |     |    |      |     |

| ITE          | Interrupt Request Flag                     |     |    |      |     |

| IUS          | Interrupt on Two Bytes                     |     |    |      |     |

| •••          | Interrupt Under Service                    |     |    |      |     |

| LC           | Country (D)                                |     |    |      |     |

| LPH          | Counter/Timer Link Controls                |     |    |      |     |

| LSB          | Latch on Pattern Match                     |     |    | 1    |     |

| 0.00         | Least-Significant Bit                      |     |    |      |     |

| IIE          |                                            |     |    | -    |     |

| MR           | Master Interrupt Enable                    |     |    |      |     |

| ISB          | Memory-Management Registers                |     |    |      |     |

| 138          | Nost-Significant Bit                       |     |    |      |     |

| V            | No Vector                                  |     |    |      |     |

|              |                                            |     |    |      |     |

| DT           | Online Debugging Technique                 |     |    |      |     |

| NE           | Single-Level VMEbus Arbiter                |     |    |      |     |

| RE           | Output Register Empty                      |     |    |      |     |

|              |                                            |     |    |      |     |

| A VIS        | Port A Vector Includes Status              |     |    |      |     |

| NE .         | Port A Enable                              |     |    |      |     |

| I.           | Programmable Array Logic                   |     |    |      |     |

| R            | Page Address Register                      |     |    |      |     |

| VIS          | Port B Vector Includes Status              |     |    |      |     |

| 3            | Port B Enable                              |     |    |      |     |

|              | Program Counter Register                   |     |    |      |     |

| E            | Port C Enable                              |     | •  |      |     |

| R            | Page Description Register                  |     |    |      |     |

| R            | Processor Error Register                   |     |    |      |     |

|              | Periodic Interrupt Flag                    |     |    |      |     |

| E            | Periodic Interrupt Flag                    |     |    |      |     |

| RQ           | Program Interrupt Enable                   |     |    |      |     |

|              | Program Interrupt Request Register         |     |    |      |     |

|              | Port Link Control                          |     |    |      |     |

|              | Pattern Mask Registers                     |     |    |      |     |

|              | Pattern Match Flag                         |     |    |      |     |

|              | Pattern-Node Specification Bit<br>Power OK |     |    |      |     |

|              |                                            |     |    |      |     |

|              |                                            |     |    |      |     |

| Abbreviation                        | Means                                                                                                                                                                                                           |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PP<br>PRI<br>PS<br>PSW<br>PT<br>PTS | Pattern Polarity Registers Priority Arbiter Power Sense Pin Processor Status Word Register Pattern Transition Registers Port-Type Select                                                                        |

| RBUF RCC RCSR REB ROR RRS RTC RRD   | Receiver Buffer Register Read Counter Control Receiver Control/Status Register Retrigger Enable Bit Release on Request Round-Robin Sequence Real-Time Clock Release When Done Request/Wait L Specification Bits |

| B<br>IO<br>QN<br>QNE                | Single-Buffer Hode<br>Special Input/Output<br>Square-Have Generator<br>Square Nave Enable                                                                                                                       |

| ART<br>F<br>IB                      | Universal Asynchronous Receiver/Transmitter Update-Ended Interrupt Flag Update-Ended Interrupt Enable                                                                                                           |

| RTA                                 | Valid RAM and Time                                                                                                                                                                                              |

| BOF                                 | Transmitter Buffer Register<br>Transmitter Control/Status Register                                                                                                                                              |

# 2. INSTALLATION

#### 2.1 INTRODUCTION

This chapter describes how to unpack, configure, and install the VME CPU Jll in a standard VME backplane.

## 2.2 UNPACKING THE VME CPU J11

Unpack the VME CPU Jll from the shipping carton. Be sure that everything on the packing list is present. Save the packing material for storing or reshipping the equipment, if necessary.

NOTE: If the shipping carton is damaged upon receipt, unpack and inspect this equipment in the presence of the carrier's agent.

#### 2.3 CONFIGURATION

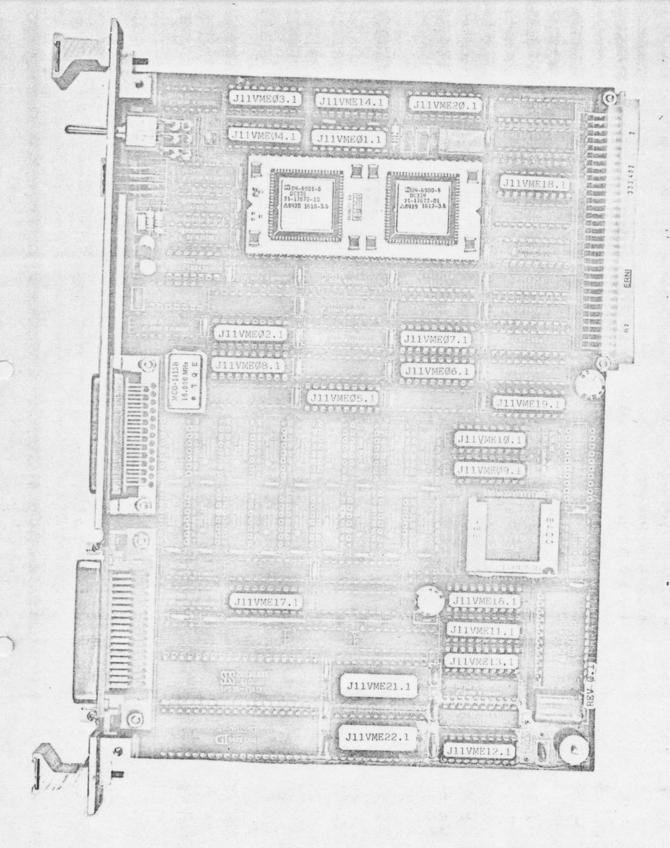

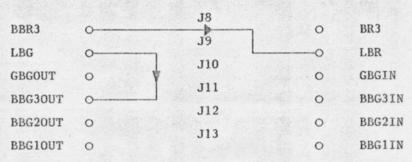

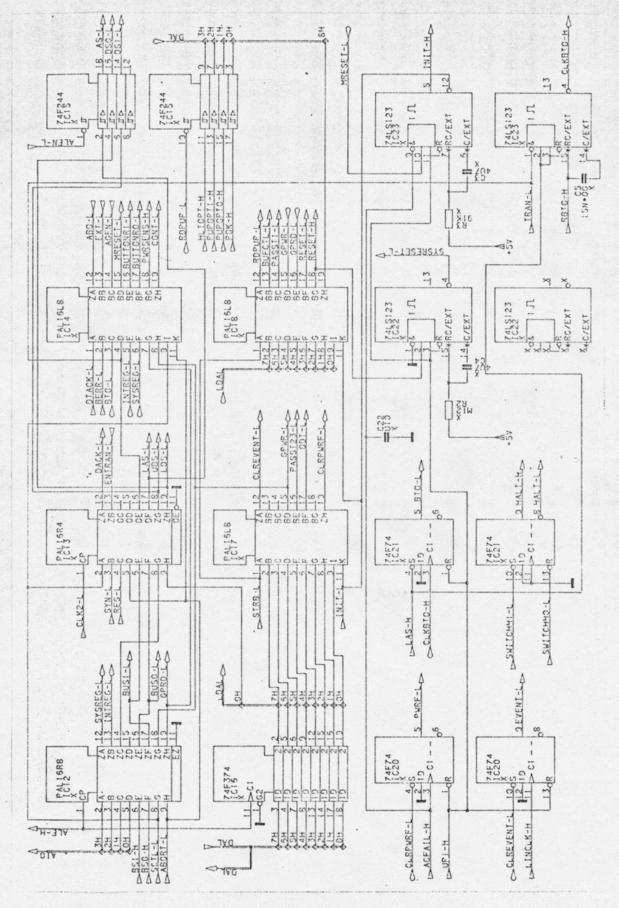

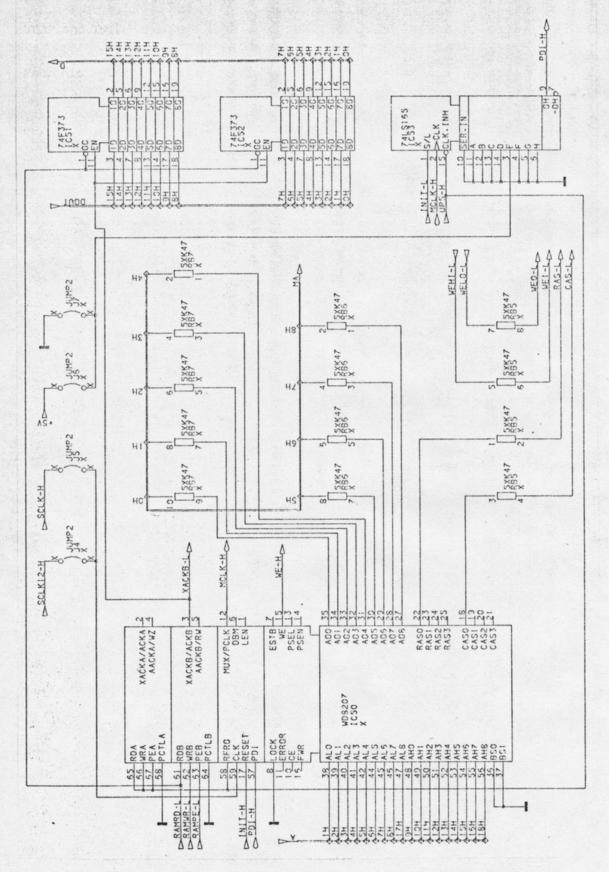

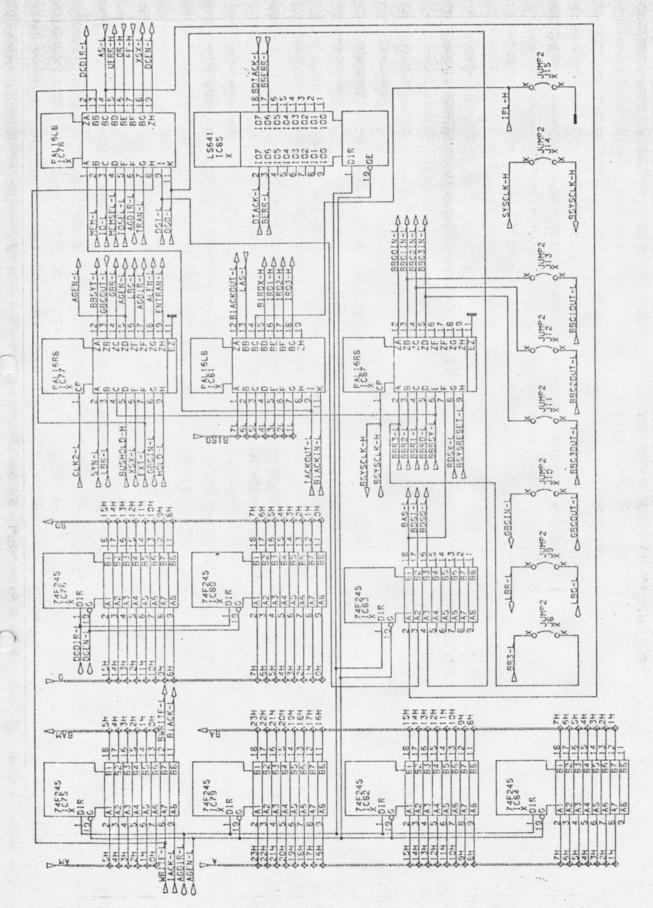

VME CPU J11 contains a number of features which you can select through jumpers and PALs. Figure 2-1 shows the location of the configurable jumpers and PALs.

Figure 2-1. VME CPU J11 Configurable Jumpers and PALs

When you receive the VME CPU J11, the following options are factory-configured:

- \* Auto-Boot

- \* ODT-HALT

- \* ROR, BR3

- \* IH (4:7)

- \* BSYSCLK out

- \* 16 MHz DRAMC Clock

- \* 512KB Memory

- \* ONE Arbiter Option

#### 2.3.1 POWER-UP OPTIONS

Power-up options are selected by jumpers J2 and J3 (Figure 2-1). Table 2-1 lists the jumper configurations for the available power-up options.

Table 2-1. VME CPU J11 Power-Up Configurations

| Option       | J2        | J3        | Function                |

|--------------|-----------|-----------|-------------------------|

| Auto-boot    | Removed   | Installed | PC at 173000, PSH = 340 |

| ODT-boot     | Installed | Renoved   | Micro-ODT, PSW = 0      |

| Restart-Boot | Installed | Installed | PC at 24, PSW = 26      |

#### 2.3.1.1 RESTART-BOOT

If you select this option, the processor reads physical memory locations 24 and 26 and loads data into the Program Counter (PC) and Processor Status Word (PSW) Registers, respectively, when the power-up sequence is executing.

The processor either services pending interrupts or starts program execution, beginning at the memory location pointed to by the Program Counter.

NOTE: Battery backup is required for this option.

## 2.3.1.2 ODT-BOOT

When you select this option, the processor unconditionally enters micro-ODT mode with the Processor Status Word Register cleared. All pending service conditions are ignored.

## 2.3.1.3 AUTO-BOOT

When you select this option, the processor sets the Program Counter to 173000 and the Processor Status Word Register to 340. The processor then either services pending interrupts or starts program execution, beginning at the memory location pointed to by the Program Counter. The changeable bootstrap EPROMS (IC29 and IC30) are selected by addresses 173000 through 173777, thus making it possible to choose different types of boot devices.

## 2.3.2 HALT OPTIONS

HALT options are selected by the J1 jumper (Figure 2-1). The HALT option determines the action taken after a HALT instruction is executed in kernel mode. Table 2-2 lists the jumper configuration for the available HALT options.

Table 2-2. VME CPU J11 HALT Configurations

| Option    | J1        | Function       |

|-----------|-----------|----------------|

| ODT-BALT  | Installed | Micro-ODT mode |

| TRAP-BALT | Removed   | Trap 4         |

#### 2.3.2.1 ODT-HALT

When you use this option, the processor enters the micro-ODT mode. The processor checks the POK bit before checking the HALT option at the end of a HALT instruction. If this bit is not set when the processor checks, the option is not recognized and the processor loops until POK is asserted and the power-up sequence is initiated.

## 2.3.2.2 TRAP-HALT

The processor traps to location 4 in the Kernel data space and sets bit 07 (illegal HALT) of the CPU Error Register.

#### 2.3.3 DRAMC SPEED OPTIONS

The Memory Controller can be adapted to two different speeds to accommodate RAMs with different access time.

The  $16~\mathrm{MHz}$  clock signal can be used with RAMs with an access time of  $100~\mathrm{ns}$ .

The 8 MHz clock signal can be used with RAMs with an access time of 250 ns.

Table 2-3 shows the jumper installation for DRAM speed selection. (You cannot use combinations which are not shown in Table 2-3.)

Table 2-3. VME CPU J11 DRAM Speed Options

| Option         | J4        | J5        | J6        | J7        |      |

|----------------|-----------|-----------|-----------|-----------|------|

| 16 MHz, 100 ms | Removed   | Installed | Removed   | Installed | .6 % |

| 8 MBz, 250 ms  | Installed | Removed   | Installed | Removed   |      |

#### 2.3.4 SIZE-SELECT OPTION

The SIZE-Select Option is used to choose a local memory size of 128KB or 512KB.

Memory size is selected by the changeable PAL 16L8 (IC26). There are two different patterns available: PAT09A and PAT09B. Table 2-4 shows the appropriate PALs for the selected size.

Table 2-4. The SIZE-Select Option

| IC26   | Size  |  |

|--------|-------|--|

| PATOSA | 512KB |  |

| PAT09B | 128KB |  |

#### 2.3.5 ARBITER OPTIONS

There are 2 arbiter options for controlling the arbitration system:

- \* PRI (Priority Arbiter)

- \* ONE (Single-Level VMEbus Arbiter)

#### 2.3.5.1 PRI

The Priority Arbiter (PRI) always assigns the bus on a fixed priority basis, in which each of four bus-request lines is assigned a fixed priority, from the highest to lowest (BR3 to BRO).

In this configuration, the board requests the VMEbus on the BR3 (highest) level. Local memory can be accessed on bus-request level 2 (BR2) or 1 (BR1), as specified by the jumpers.

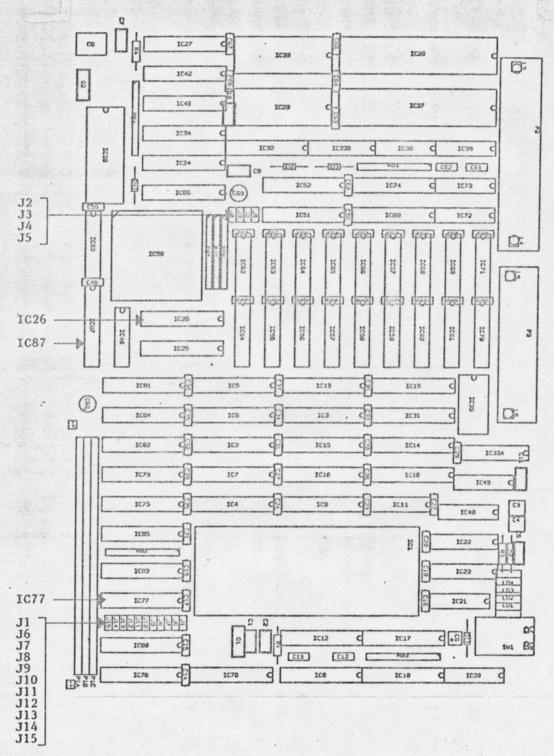

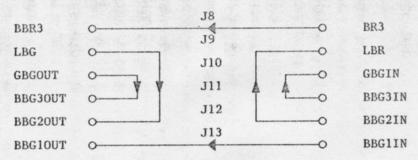

Figures 2-2 and 2-3 show the jumper configurations for the Priority Arbiter (PRI) option. The Arbitrator (PAL 16R8 - IC87) must also be installed when you select this option.

Figure 2-2. Jumper Configuration for Local Memory Access on the BR1 Level

Figure 2-3. Jumper Configuration for Local Memory Access on the BR2 Level

#### 2.3.5.2 ONE

Single-Level VMEbus Arbiter (ONE) only honors requests on the highest level (BR3). Prioritizing is controlled by the BG3IN - BG3OUT daisy chain. The highest priority has the nearest board, while the board itself has the lowest priority; any bus request overrides the board request.

Figure 2-4 shows the jumper configuration for the ONE Arbiter option. The Arbitrator (PAL 16R8 - IC87) must be removed when you use this option.

Figure 2-4. Jumper Configuration for the ONE Arbiter Option

#### 2.3.6 REQUESTOR OPTIONS

There are two Requestor options available:

- \* ROR (Release on Request)

- \* RWD (Release when Done)

These options are selected by the changeable PAL 16R8 (IC77). Table 2-5 shows the configuration for each option.

Table 2-5. VME CPU J11 Requestor Configurations

| Option | 1077   | 1087      |  |

|--------|--------|-----------|--|

| ROR    | PAT18A | Removed   |  |

| RWD    | PAT18B | Installed |  |

#### 2.3.6.1 ROR

The Release on Request (ROR) Requestor does not release the VMEbus each cycle. It monitors the BR3 line and releases only when another bus request is pending. The Arbitrator (PAL 16R8 - IC87) must be removed for this option.

#### 2.3.6.2 RWD

The Release when Done (RWD) Requestor requests the VMEbus on BR3 and releases it when another bus request is pending or when its master no longer wants the bus. The Arbitrator (PAL 16R8 - IC87) must be installed when you select this option.

## 2.3.7 INTERRUPT HANDLER OPTIONS

Interrupt Handler options determine which interrupt request lines the Interrupt Handler will respond to. The Interrupt Handler can operate in two different modes:

- \* Four-Level Interrupt Mode

- \* Three-Level Interrupt Mode

In the four-level interrupt mode, only levels 4-7 are supported and are assigned to processor interrupt priority levels 4-7, respectively.

In the three-level interrupt mode, only levels 1-3 are supported and are assigned to processor interrupt priority levels 5-7, respectively.

In both modes, the on-board I/O devices (serial port, parallel port, timers, and clock alarm) are assigned to processor interrupt priority level 4 and have the highest priority on this level. The system clock is always assigned to processor interrupt priority level 6. The data contained in the interrupting devices' status/ID byte is used to determined the appropriate vector address and is set to longword boundary.

Table 2-6 shows the jumper configuration for the Interrupt Handler options.

Table 2-6. VME CPU J11 Interrupt Handler Options

| Option .                   | J15       |  |

|----------------------------|-----------|--|

| Four-Level Interrupt Mode  | Removed   |  |

| Three-Level Interrupt Mode | Installed |  |

#### 2.3.8 BSYSCLK

The system clock (BSYSCLK) is an independent, non-gated, fixed-frequency, 16 MHz, 50% duty-cycle signal. It can be used to generate on-board delays or timing functions. Install the J14 jumper to obtain this function.

#### 2.4 BOARD INSTALLATION

The VME CPU J11 double-height board is installed in a standard VME double-height backplane. The CPU board is normally installed into the first of nine slots (counting from left to right). Every additional CPU board is installed in the next slot to the right of installed boards.

When the board is ready for installation:

- 1. Turn off power to the equipment.

- CAUTION: Inserting or removing boards while power is on can seriously damage board components.

- Hold the board so that the components are on the right side of the board and carefully slide the board into the left-most open slot.

- Be sure that the board is properly seated in the connectors on the backplane and fasten it into the chassis with the screws provided.

- Connect other components (terminal, printer, etc.), if necessary (using the instructions in the next sections).

- . 5. Turn on the power to the equipment.

#### 2.4.1 CONSOLE TERMINAL CONNECTION

Use a standard 25-pin RS-232C EIA connector (DTE) to connect a Console Terminal to the VME CPU J11 board, for communication with the processor through an asynchronous, full-duplex, serial line.

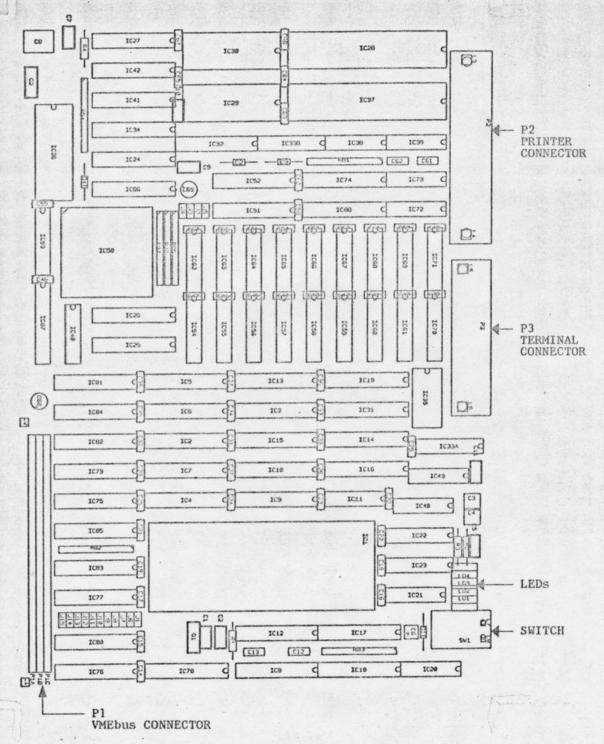

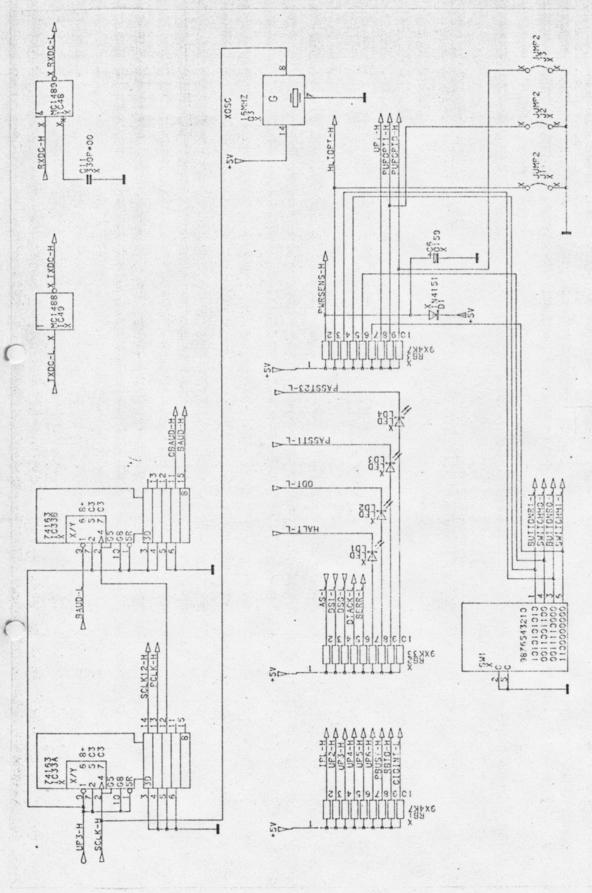

The connector (P3) is installed on the front edge of the board under the LED indicators (Figure 2-5).

Table 2-7 lists the pin specifications for the console connector (P3).

Figure 2-5. VME CPU J11 Switch, LEDs, and Peripheral Connectors

Table 2-7. Pin Specifications for the Console Connector

| Pin | Specification  |  |

|-----|----------------|--|

| 1   | Protective GND |  |

| 2   | Tx Data        |  |

| 3   | Rx Data        |  |

| 7   | Signal GND     |  |

#### 2.4.2 PRINTER CONNECTION

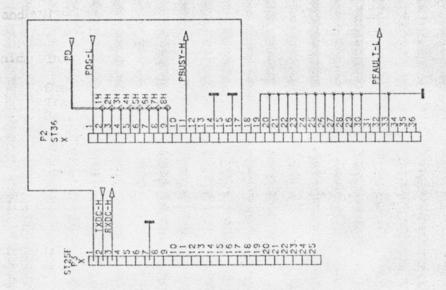

You can also connect a printer through a standard parallel interface to the VME CPU J11. There is a 36-pin Centronics connector (P2) on the front edge of the board under the RS-232C connector (Figure 2-5).

Table  $\,$  2-8 lists the pin specifications for the 36-pin Centronics connector.

Table 2-8. Pin Specifications for the Centronics Connector

| Pin               | Specification                                                                                                   |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------|--|

| 1 10 <sup>±</sup> | POS L                                                                                                           |  |

| 2 202             | PO 1 B                                                                                                          |  |

| 4, 20             | 그리고 그리고 그리고 그리고 그리고 그리고 있는데 그리고 있다면 그리고 |  |

| 3, 21,            | PD 2 B                                                                                                          |  |

| 4. 22             | PD 3 8                                                                                                          |  |

| 5, 23*            | PD 4 B                                                                                                          |  |

| 6, 24°            | PD 5 B                                                                                                          |  |

| 7, 25             | PD 6 B                                                                                                          |  |

| 8, 26             | PD 7 B                                                                                                          |  |

| 9, 27             | PD 8 B                                                                                                          |  |

| 11, 29*           | PBUSY 8                                                                                                         |  |

| 32                | PEAULT L                                                                                                        |  |

| 17                | Protective GND                                                                                                  |  |

| 14, 16            | Signal GND                                                                                                      |  |

<sup>\*</sup>Note: Second pin number indicates twisted-pair return line.

#### 2.4.3 VMEbus CONNECTION

You connect the VME CPU J11 to the VMEbus through the 96-pin P1 connector (Figure 2-5).

Table 2-9 lists the pin specifications for the Pl connector.

Table 2-9. Pin Specifications for the P1 Connector

|        | Row        | Row       | Row          | 2.5 (0.05) |  |

|--------|------------|-----------|--------------|------------|--|

| Pin    | Signal     | Signal    | Signal       |            |  |

| Number | Mnenonic   | Mnemonic  | Mnemonic     |            |  |

| 1      | BDO H      | BBBSY L   | BDB H        |            |  |

| 2      | BD1 B      |           | BD9 H        |            |  |

| 3      | BD2 H      | BACFAIL L | BD10 B       |            |  |

| 4      | BD3 B      | BBGOIN L  | BD11 B       |            |  |

| 5      | BD4 H      | BBGCOUT L | BD12 H       |            |  |

| 6      | BD5 H      | BBG1IN L  | BD13 B       |            |  |

| 7      | BD6 H      | BBG10UT L | BD14 H       |            |  |

| 8      | BD7 B      | BBG2IN L  | BD15 B       |            |  |

| 9      | GND        | BBG20UT L | GND          |            |  |

| 10     | BSYSCLK H  | BBG3IN L  | BSYSFAIL L   |            |  |

| 11     | GND        | BBG30UT L | BBERR L      |            |  |

| 12     | BDS1 L     | BBRO L    | BSYSRESET L  |            |  |

| 13     | BDS0 L     | BBR1 L    | 0010110001 0 |            |  |

| 14     | BURITE L   | BBR2 L    | BANS B       |            |  |

| 15     | GND        | BBR3 L    | BA23 E       |            |  |

| 16     | BDTACK L   | BANO H    | BA22 B       |            |  |

| 17     | GND        | BAN1 H    | BA21 B       |            |  |

| 18     | BAS L      | BAN2 H    | BA20 B       |            |  |

| 19     | GND .      | BAH3 B    | BA19 B       |            |  |

| 20     | BJACK L    | GND       | BA18 H       |            |  |

| 21     | BJACKIN L  |           | BA17 B       |            |  |

| 22     | BJACKOUT L |           | BA16 B       |            |  |

| 23     | BANA B     | GND       | BA15 B       |            |  |

| 24     | BA7 B      | BIRQ7 L   | BA14 B       |            |  |

| 25     | BA6 H      | BIRQ6 L   | BA13 B       |            |  |

| 26     | BAS H      | BIRQ5 L   | BA12 B       |            |  |

| 27     | BA4 B      | BIRQ4 L   | BA11 B       |            |  |

| 8      | BA3 H -    | BIRQ3 L   | BA10 H       |            |  |

| 9      | BA2 R      | BIRQ2 L   | BA9 B        |            |  |

| 0      | BA1 H      | BIRQ1 L   | BAS H        |            |  |

| 1      | -12 V      | +5 V B    | +12 V        |            |  |

| 2      | +5 V       | +5 V      | +5 V         |            |  |

# 2.4.4 MAINTENANCE INDICATORS AND SWITCHES

There is a three-position switch and four LED maintenance indicators on the VME CPU J11 board (Figure 2-5).

The three-position switch has three functions:

- \* Top position = (Unstable) Release to execute the INIT function

- \* Middle position = (Stable) Normal operating position

- \* Bottom position = (Stable) Execute the HALT function

The four LEDs (below the switch) monitor operating status and are useful when troubleshooting the system.

Table 2-10 shows the functions of the LEDs. Table 2-11 shows typical LED readings during different types of system failures.

Table 2-10. VME CPU J11 LED Functions

| LED   | Status | Function                                                                                                                                      |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| D1    | Off    | Normal operation                                                                                                                              |

|       | 0 n    | BALT indicator (Switch in BALT position)                                                                                                      |

| D2    | Off    | Normal operation                                                                                                                              |

|       | On     | Operating in micro-ODT mode                                                                                                                   |

| D3 On |        | Normal operation                                                                                                                              |

|       | Off    | The CPU Error Register is not accessible for read or write transactions. The microcode is not running.                                        |

| D4    | 0 n    | Normal operation                                                                                                                              |

|       | Off    | Module attempted to read location 17777560 and timed out (the serial interface is not responding).                                            |

|       |        | Module attempted to read location 0 and timed out or attempted to read location 17777700 and did not time out (memory system not responding). |

Table 2-11. LED Readings During System Failure

| D3  | D4  | Probable Cause of Failure                   |  |

|-----|-----|---------------------------------------------|--|

| 0 n | On  | Console terminal, serial interface          |  |

| 0 n | Off | Memory, bus time-out, serial interface      |  |

| Off | 0 n | CPU                                         |  |

| Off | Off | CPO, memory, bus time-out, serial interface |  |

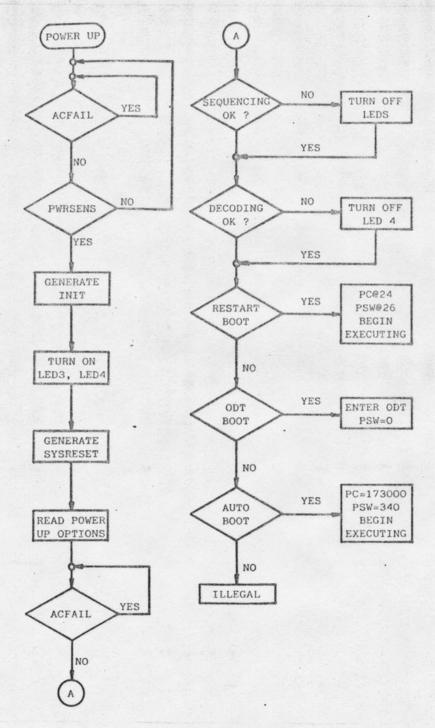

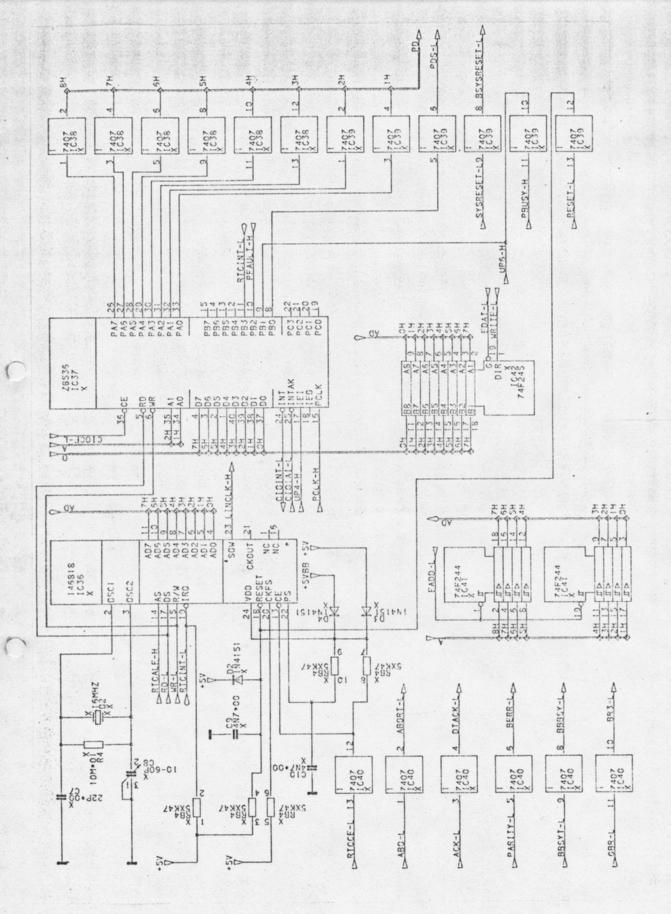

#### 2.4.4.1 POWER-UP SEQUENCE

Figure 2-6 shows what happens when power is turned on.

Figure 2-6. VME CPU J11 Power-Up Sequence

### 2.4.4.2 POWER-DOWN SEQUENCE

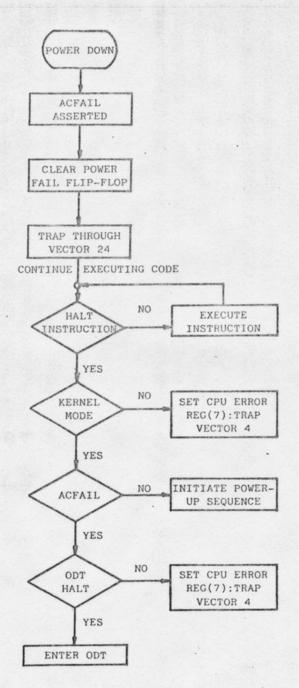

Figure 2-7 shows what happens when power is turned off.

Figure 2-7. VME CPU J11 Power-Down Sequence

### 2.5 CONSOLE ONLINE DEBUGGING TECHNIQUE (ODT)

ODT mode is assigned by an "0" prompt at the console terminal. It accepts 22-bit addresses.

Table 2-12 lists commands available in ODT mode.

Table 2-12. ODT Mode Commands

| Connand                          | Key            | Function                                                                 |

|----------------------------------|----------------|--------------------------------------------------------------------------|

| Slash                            | (/)            | Print the contents of a specified location.                              |

| Return                           | (CR)           | Close an open location.                                                  |

| Line feed                        | (LF)           | Close an open location and open the next contiguous location.            |

| Internal Register designator     | (\$) or<br>(R) | Open a specific processor register.                                      |

| Processor Status Word designator | (5)            | Open the Processor Status Register (must follow the (\$> or (R) command. |

| So -                             | (G)            | Begin executing a program.                                               |

| Proceed                          | (P)            | Resume executing a program.                                              |

| Binary dump                      | (Ctrl)(S)      | (Manufacturing use only)                                                 |

#### 2.5.1 EXITING THE MICRO-ODT SEQUENCE

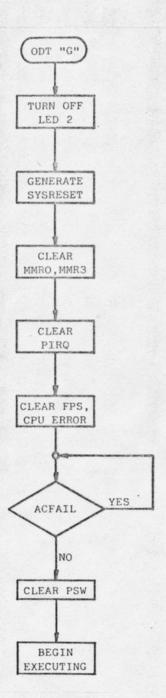

Figure 2-8 shows what happens when the <G> command is used to exit the micro-ODT sequence.

Figure 2-8. The Exit Micro-ODT Sequence

#### 3. ARCHITECTURE

## 3.1 INTRODUCTION

VME CPU J11 is designed for use in high-speed, real-time applications and for multiuser, multitasking environments.

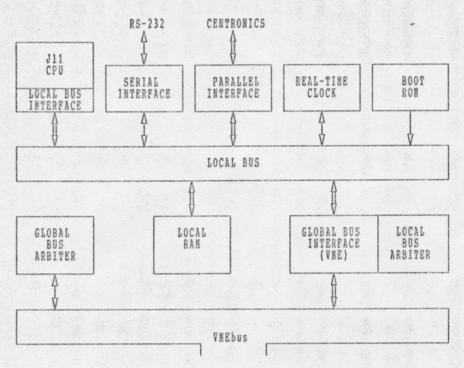

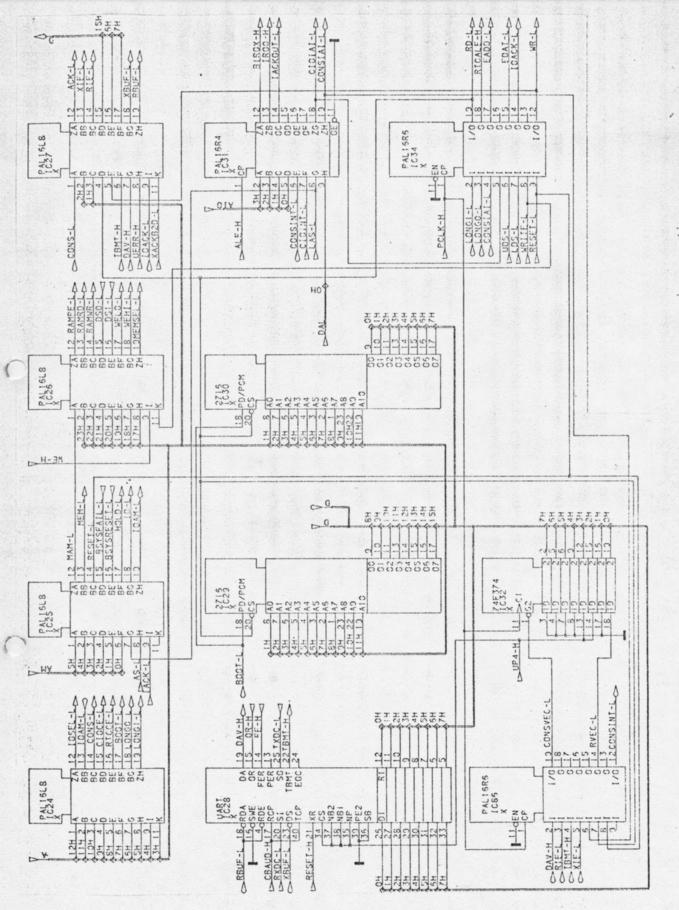

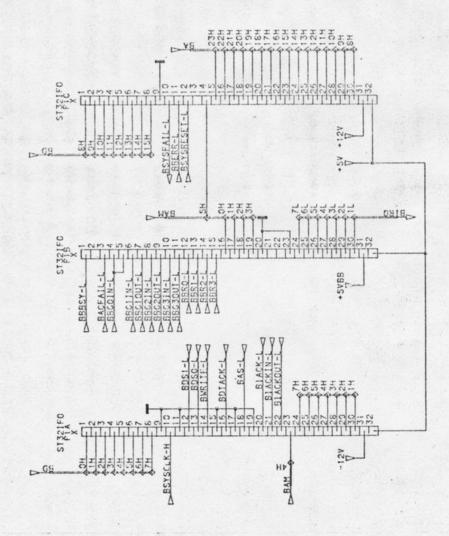

Figure 3-1 provides a simplified overview of the module architecture.

The CPU communicates with local memory and local devices (serial interface, parallel interface, real-time clock, and boot memory) through the local bus.

The local bus is connected to the VMEbus through the VMEbus interface. Access to the local bus is controlled by the local bus arbiter; access to the VMEbus is controlled by the VMEbus arbiter.

Local memory can be accessed from the VMEbus and on-board CPU, but local devices can be accessed only by the on-board CPU.

## 3.2 THE CENTRAL PROCESSING UNIT

The DEC DCJ11 is a 16-bit microprocessor. It uses VLSI CMOS technology to operate with 1 Watt of power dissipation. On-chip clock generation, microdiagnostic and console octal debugging permit easy hardware interface and maintenance.

A four-level pipeline and instruction prefetch allow overlapping between internal operations and bus transactions.

The DCJ11 chip includes a 64-bit floating point section and memory management unit. The 32-bit internal data path optimizes the performance of floating-point arithmetic. It also includes an orthogonal instruction set compatible with the PDP-11 and General Purpose Registers (GPR) for more efficient programming.

Memory management provides three levels of memory protection for multiuser and multitasking environments. It also extends a 128K direct-address range into a 4 MB physical-address range.

Figure 3-1. VME CPU J11 Architecture

#### 3.3 LOCAL MEMORY

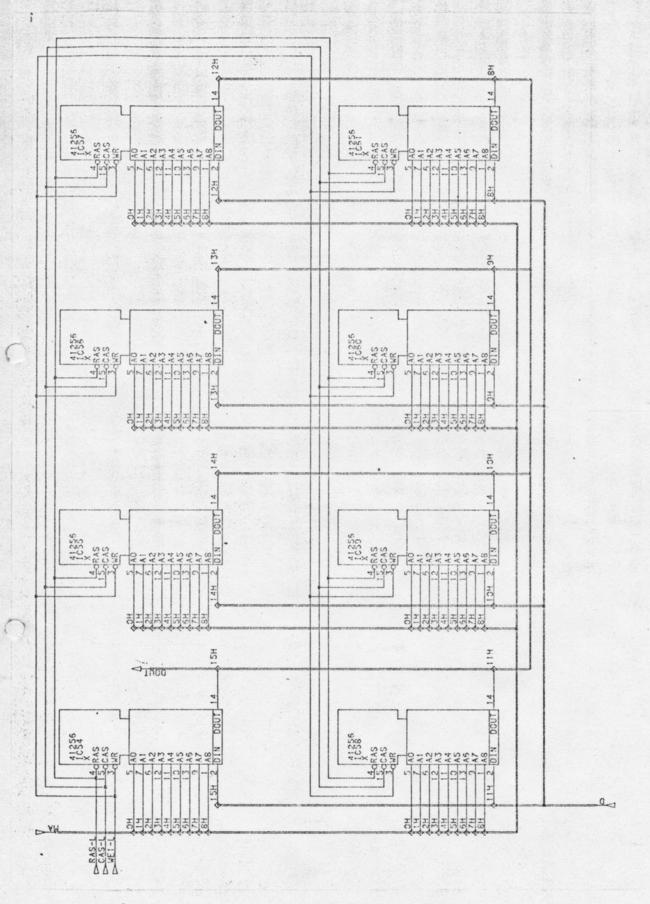

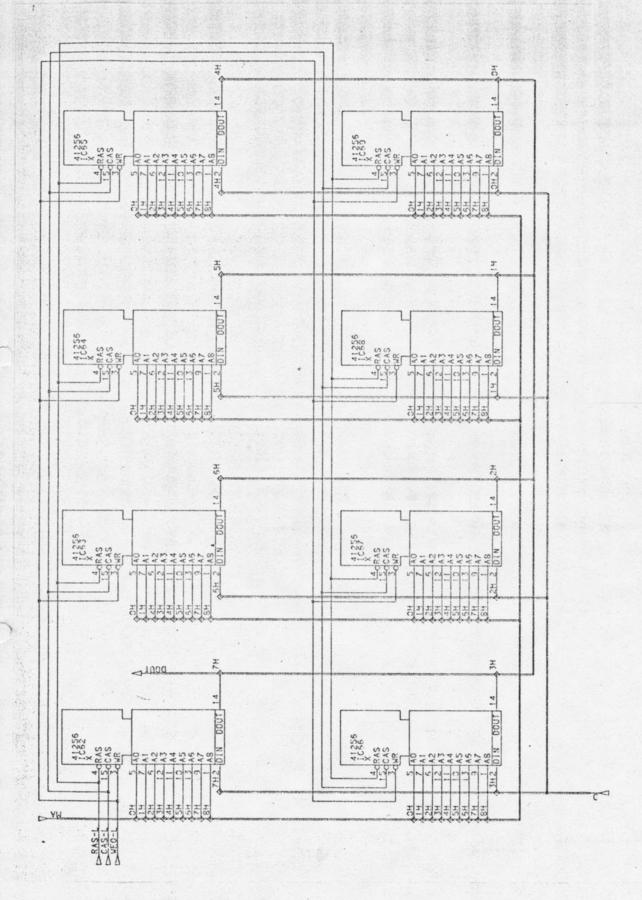

Local memory is connected to the local bus, which can be accessed either from the on-board CPU or an external DMA device. The Intel 8207 dynamic RAM controller provides the necessary signals to address, refresh, and directly drive 64K or 256K dynamic RAM.

The controller is programmed to run in asynchronous mode with either a 16 MHz or 8 MHz clock.

Local memory size is 128K or 512K, depending on the selected RAM capacity (64Kxl or 256Kxl). Flexible address decoding (provided by a PAL) also assures easy address relocation and size selection, when necessary.

Byte parity control is also available to detect parity errors in local memory, thereby increasing the reliability of the system. Parity can be disabled, if desired, for easier testing and servicing.

#### 3.4 SERIAL INTERFACE

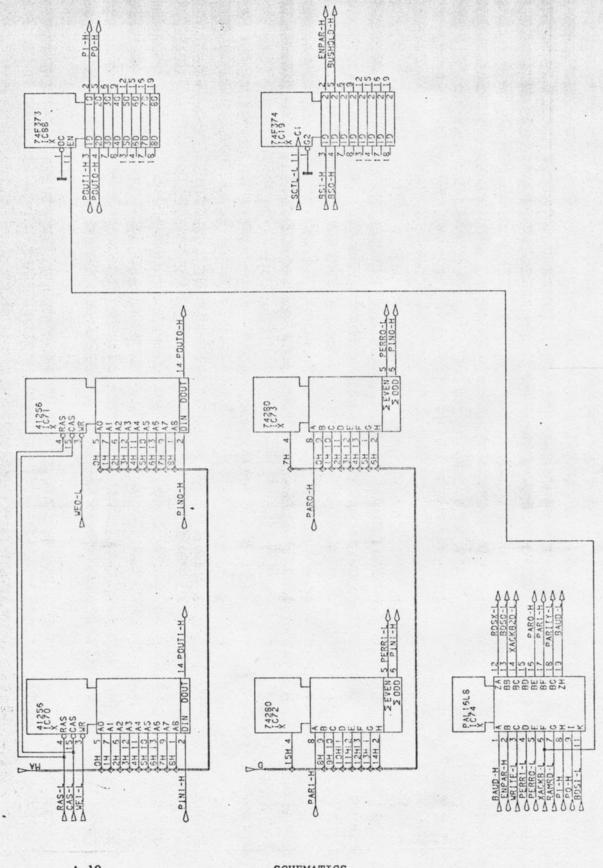

The serial, asynchronous interface is a DL-11 device emulation (see the programming model).

Serial-to-parallel conversion is done by the AY-3-1015D Universal Asynchronous Receiver/Transmitter (UART). The character format of serial data is fixed at 8 bits per character, no parity, 1 stop bit, 9600-baud transmission, RS-232C interface.

The Status Control Registers and Interrupt Handler are emulated by PALs. The interrupt vectors are fixed, and are standard PDP-11 console vectors.

The serial line serves as a console terminal port which supports ODT functions so there is no need for program initialization. It uses the standard PDP-11 console address.

The serial line can be accessed only by the on-board CPU, not by external devices. When a multiprocessor configuration is used, all CPU boards handle the console terminal, including ODT functions, in the same way.

#### 3.5 PARALLEL INTERFACE

The parallel interface is designed by the general-purpose peripheral integrated circuit CIO Z8536. This device contains three I/O ports and three counter/timers.

The I/O ports serve as parallel printer ports with a Centronics handshake.

Counter/timers are for general use in real-time applications.

The parallel interface can be accessed only by the on-board CPU. In multiprocessor configurations, all CPUs handle the parallel interface in the same way.

#### 3.5.1 PARALLEL PRINTER PORT

Port A is an 8-bit output port for printer data lines. It must be programmed as an output-bit-mode port.

Port B is used for printer handshake (Centronics-compatible), including data strobe, busy, and fault; and is also used as an interrupt source for printer acknowledgements (busy).

An interrupt vector can be loaded. All output lines are buffered with open collector drivers.

### 3.5.2 COUNTER/TIMERS

The three independent 16-bit counter/timers consist of:

- \* A 16-bit down-counter that can be preset

- \* A 16-bit Time Constant Register

- \* A 16-bit Current Counter Register

- \* An 8-bit Mode Specification Register

- \* An 8-bit Command/Status Register

- \* A common 8-bit Vector Register

Only Timer Mode can be used (internal clock). Trigger input, gate input, and counter/timer output cannot be used.

#### 3.6 REAL-TIME CLOCK

The real-time clock (RTC) is provided by the MC146818 CMOS low-power integrated circuit.

The real-time clock enables the VME CPU J11 to be used for real-time applications.

Three features are available:

- \* A complete time-of-day clock with alarm and onehundred-year calendar

- \* A programmable periodic interrupt and square-wave generator

- \* 50 bytes of static RAM

External battery backup from the VMEbus is provided to keep the time-of-day clock running and maintain data integrity in the RAM.

The real-time clock can be accessed only by the on-board CPU; in multiprocessor configurations all CPU boards handle this device in the same way.

### 3.6.1 LINE CLOCK GENERATOR

The square-wave generator (SQW) is used as a line clock. You can alter the frequency and output enable of the square-wave generator by programming Register A. The square-wave signal (line clock) can be turned on and off using a bit in Register B (line clock interrupt enable/disable). When power is turned on (or a RESET instruction received), the square-wave signal is disabled.

#### 3.6.2 TIME-OF-DAY CLOCK AND TIME-OF-DAY ALARM

The processor program obtains time and calendar information by reading the appropriate RAM locations. The program can initialize the time, calendar, and alarm by writing data into these RAM locations. The contents of the time, calendar, and alarm can be either binary or binary coded decimal (BCD). The Valid RAM and Time (VRTA) bit in Register D indicates the condition of the contents of the RAM.

#### 3.6.3 GENERAL-PURPOSE DATA MEMORY

The 50 bytes of user RAM serve the need for low-power CMOS battery backup storage. RAM memory can be used to store non-volatile data that must be retained when the main power is off.

#### 3.7 BOOT LOGIC

The two changeable boot EPROMs are accessible for the boot-up procedure and diagnostic purposes. The EPROMs are directly accessed when power is turned on, if you use the Auto-Boot power-up option (Chapter 2.3.1.3).

Changeability of EPROMs allows you to choose different types of boot devices. Like other on-board I/O devices, the boot option is not accessible to external devices. For this reason, the boot address can be identical for all CPU boards in multiprocessor systems.

#### 3.8 INTERRUPT HANDLER

The VMEbus consists of 7 interrupt-request levels, organized in a vertical-priority manner. (Level 7 is the highest-priority level and level 1, the lowest.)

Interrupt Requestors on the same level are daisy-chain connected. The first Requester to the far left of the Interrupt Handler has the highest priority and the last Requestor on the right has the lowest priority.

There can be one (single-handler system) or more (distributed handler system) Interrupt Handlers on the VMEbus. VME CPU J11 supports up to 4 interrupt-request levels. Two options are jumper selectable: four-level interrupt mode and three-level interrupt mode.

In four-level interrupt mode, levels 4-7 are supported and assigned to processor interrupt priority levels 4-7, respectively.

In three-level mode, levels 1-3 are supported and assigned to processor interrupt priority levels 5-7, respectively.

In all configurations, local devices are connected to processor-interrupt priority level 4 and have the highest priority on that level. The line clock is connected to processor-interrupt priority level 6 and has the highest priority on that level. The ID byte is first aligned with the longword boundary and then used as a vector address for the interrupt routine.

#### 3.8.1 SINGLE-HANDLER SYSTEMS

In single-handler systems, the VME CPU J11 is a supervisory processor which receives and services all VMEbus interrupts. Other processors are not required to service interrupts from the bus. You can select a four- or three-level Interrupt Handler.

#### 3.8.2 DISTRIBUTED-HANDLER SYSTEMS

In distributed handler systems, two or more processors can receive and service bus interrupts. Each co-equal processor executes part of the system executive software and services only those interrupts directed to it by other processors within the system.

There can be two VME CPU J11 modules in a system of this type: one with a four-level Interrupt Handler, and the other with a three-level Interrupt Handler.

#### 3.9 BUS ARBITRATION

The VMEbus contains four bus-request levels, organized in a vertical priority. There are three Arbiter options:

- \* Single-Level Arbiter (ONE)

- \* Fixed Priority (PRI)

- \* Round-Robin Sequence (RRS)

Only the ONE and PRI options (four-level arbitration) are available on the VME CPU J11.

### 3.9.1 SINGLE-LEVEL ARBITRATION (LOCAL ARBITER)

Single-level arbitration only services bus requests on the BR3 level. Priority is controlled by a daisy-chain connection. Any bus request overrides the board request. This option is selected when you use the VME CPU Jll in a single-processor configuration.

### 3.9.2 FOUR-LEVEL ARBITRATION (GLOBAL ARBITER)

Four-level arbitration services all four bus-request levels. The BR3 level has the highest priority and BRO, the lowest . You use this option when you use two VME CPU Jll modules in the same system.

First, the local bus is accessed on the BR2 level and second, on the BR1 level. All modules, including CPUs, request the VMEbus on the BR3 level. This allows simultaneous operation of both processors on their own local memory and other modules on the VMEbus; or, when one processor is running on local memory, a DMA transfer can be done in another's local memory.

### 4. PROGRAMMING MODEL

### 4.1 VME CPU J11 PROGRAMMING MODEL

Figure 4-1 shows the visible registers on the VME CPU J11. These registers include the General-Purpose, System-Control, Memory-System, Memory-Management, and Floating-Point Registers.

| GENERAL PURPOSE                                | SYSTEM CONTROL     | MEMORY SYSTEM                        |

|------------------------------------------------|--------------------|--------------------------------------|

| R0 R0' RSP SSP SSP USP R3' R4' R5' PC          | PSH PIRQ CPU ERROR | PAR CTRL                             |

| FLOATING POINT                                 | MEMORY             | BARAGERERT                           |

| FPS FEC FEA                                    | REEG ERRI          | MHRZ MHR3                            |

| ACCUMULATORS (64 BII)  ACU ACI ACZ AC3 AC4 AC5 |                    | 01) USER(11) 0 1 2 3 4 5 6 7 PAR PDR |

Figure 4-1. Visible Registers

### 4.1.1 GENERAL-PURPOSE REGISTERS

There are 16 General-Purpose Registers (GPR) (Figure 4-1):

- \* A dual set of six registers (RO R5 and RO' R5')

- \* Three stack pointers which correspond to the three processor modes (kernel, supervisor, and user)

- \* A Program Counter (PC)

Only one stack pointer is visible at any given time.

The two six-register sets (RO - R5 and RO' - R5') cannot be used simultaneously. The group currently in use is selected by bit 11 in the Processor Status Word Register (PSW).

Only 8 registers are visible at any given time.

#### 4.1.2 SYSTEM-CONTROL REGISTERS

There are three System-Control Registers:

- \* Processor Status Word Register (PSW)

- \* Program Interrupt Request Register (PIRQ)

- \* Processor Error Register (PER)

The Processor Error Register identifies the source of any trap or abort condition that caused a trap through location 4.

Table 4-1 shows the address classifications for the System-Control Registers.

Table 4-1. System-Control Register Addresses

| Address  | Register                         |  |

|----------|----------------------------------|--|

| 17777776 | Processor Status Word (PSW)      |  |

| 17777772 | Program Interrupt Request (PIRQ) |  |

| 17777766 | Processor Error (PER)            |  |

## 4.1.2.1 PROCESSOR STATUS WORD REGISTER (PSW)

Table 4-2 lists the bit description for the Processor Status Word Register.

Table 4-2. Processor Status Word Register Bit Description

| Bit     | Wane                 | Description                                                                                                               |

|---------|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| 00      | Carry<br>R/W         | Set when the previous operation causes a carry out.                                                                       |

| 01      | Overflow R/W         | Set when the previous operation results in an arithmetic overflow.                                                        |

| 02      | Zero<br>R/W          | Set when the result of the previous operation is zero.                                                                    |

| 03      | Negative<br>R/W      | Set when the result of the previous operation is negative.                                                                |

| 04      | Trap<br>R/W          | When set, the processor traps to location 14 at the end of the current instruction.                                       |

| 05 - 07 | Priority<br>R/W      | Indicates the encoded current interrupt priority level of the processor.                                                  |

| 8       | Reserved<br>R/H      | Reserved for future use.                                                                                                  |

| 09 - 10 | Unused<br>R          | Read as zeros.                                                                                                            |

| 11      | Register Set<br>R/H  | Selects a group of General-Purpose Registers. When set, the RO'-R5' group is used; when cleared, the RO-R5 group is used. |

| 12, 13  | Previous mode<br>R/H | Indicates previous processor mode:  00 = Kernel 01 = Supervisor 10 = Illegal 11 = User                                    |

| 14, 15  | Current mode R/W     | Indicates current processor mode (same as above).                                                                         |

## 4.1.2.2 PROGRAM INTERRUPT REQUEST REGISTER (PIRQ)

Table 4-3 lists the bit description for the Program Interrupt Request Register (PIRQ).

Table 4-3. Program Interrupt Request Register Bit Description

| Bit     | Name                | Description                                                                               |

|---------|---------------------|-------------------------------------------------------------------------------------------|

| 01 - 03 | Encoded Value       | The encoded value of the highest priority level set in bits 9 - 15. Same as bits 05 - 07. |

| 05 - 07 | Encoded Value<br>RO | Same as bits 01 - 03.                                                                     |

| 9       | Level 1             | Requests level 1 interrupt priority.                                                      |

| 10      | Level 2             | Requests level 2 interrupt priority.                                                      |

| 11      | Level 3<br>RM       | Requests level 3 interrupt priority.                                                      |

| 12      | Level 4             | Requests level 4 interrupt priority.                                                      |

| 13      | Level 5             | Requests level 5 interrupt priority.                                                      |

| 14      | Level 6             | Requests level 6 interrupt priority.                                                      |

| 15      | Level 7             | Requests level 7 interrupt priority.                                                      |

## 4.1.2.3 PROCESSOR ERROR REGISTER (PER)

Table 4-4 lists the bit description for the Processor Error Register.

Table 4-4. Processor Error Register Bit Description

| Bit    | Name                         | Description                                                                                                       |

|--------|------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 0 - 1  | -                            | Not used.                                                                                                         |

| 2      | Red stack violation<br>RO    | Set on red stack trap: a kernel stack push abort during an interrupt, abort, or trap sequence.                    |

| 3      | Yellow stack violation<br>RO | Set on yellow zone stack overflow trap. (Kernel mode stack references less than 400 octal.)                       |

| 4      | I/O bus time out             | Set when reference to the I/O page times out.                                                                     |

| 5      | Nonexistent memory<br>RO     | Set when a reference to main memory times out.                                                                    |

| 6      | Address Error<br>RO          | Set when word access to an odd byte address<br>or an instruction fetch from an internal<br>register is attempted. |

| 7      | Illegal Balt<br>RO           | Set when execution of a BALT instruction is attempted in user or supervisor mode.                                 |

| 8 - 15 |                              | Not used.                                                                                                         |

#### 4.1.3 MEMORY-MANAGEMENT REGISTERS

The Memory Management Unit provides three separate address spaces (Kernel, Supervisor, and User), each having different privileges and independent sets of 16-bit mapping and protection registers. Each operating mode is assigned 16 Page Descriptor Registers (PDR) and 16 Page Address Registers (PAR) to handle instruction space and data space.

Table 4-5 shows the address classifications for the Memory-Management Registers (MMR).

Table 4-5. Memory-Management Register Addresses

| Address             | Register                                    |

|---------------------|---------------------------------------------|

| 17777576            | Newory Management Status Register 2         |

| 17777574            | Memory Management Status Register 1         |

| 17777572            | Memory Management Status Register 0         |

| 17772516            | Memory Management Status Register 3         |

| 17777660 - 17777676 | User Data PAR, Registers 0 - 7              |

| 17777640 - 17777656 | User Instruction PAR, Registers 0 - 7       |

| 17777620 - 17777636 | User Data PDR, Registers 0 - 7              |

| 17777600 - 17777616 | User Instruction PDR, Registers 0 - 7       |

|                     |                                             |

| 17772360 - 17772376 | Kernel Data PAR, Registers 0 - 7            |

| 17772340 - 17772356 | Kernel Instruction PAR, Registers 0 - 7     |

| 17772320 - 17772336 | Kernel Data PDR, Registers 0 - 7            |

| 17772300 - 17772316 | Kernel Instruction PDR, Registers 0 - 7     |

|                     |                                             |

| 17772260 - 17772276 | Supervisor Data PAR, Registers 0 - 7        |

| 17772240 - 17772256 | Supervisor Instruction PAR, Registers 0 - 7 |

| 17772220 - 17772236 | Supervisor Data PDR, Registers 0 - 7        |

| 17772200 - 17772216 | Supervisor Instruction PDR, Registers 0 - 7 |

### 4.1.3.1 PAGE ADDRESS REGISTER (PAR)

Table 4-6 lists the bit description for the Page Address Register.

Table 4-6. Page Address Register Bit Description

| Bit    | Name               | Description                                                                                       |  |

|--------|--------------------|---------------------------------------------------------------------------------------------------|--|

| 0 - 15 | Page Address Field | 16-bit field which specifies the starting address of a page as a block number in physical memory. |  |

### 4.1.3.2 PAGE DESCRIPTION REGISTER (PDR)

Table 4--7 lists the bit descriptions for the Page Description Register (PDR).

Table 4-7. Page Description Register Bit Description

| Bit    | Name                    | Description                                                                                                                                                                                        |

|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      |                         | Not used.                                                                                                                                                                                          |

| 1 - 2  | Access<br>R/N           | Access control code for this page:  00 = Nonresident (abort on access)  01 = Read only (abort on writes)  10 = Not used (abort all accesses)  11 = Read/Nrite access                               |

| 3      | Expansion direction R/W | Specify direction in which the page expands. If<br>this bit is clear, the page expands upwards from<br>block number 0 to include blocks with higher<br>addresses.                                  |

| 4, 5   |                         | Not used.                                                                                                                                                                                          |

| 6      | Page Written<br>RO      | This bit is set to indicate a modified page. The "R" bit is automatically cleared when the PAR or PDR of that page is written into.                                                                |

| 7      | •                       | Not used.                                                                                                                                                                                          |